SDRAM 详解

2013-07-18 17:46阅读:

SDRAM(Synchronous Dynamic Random Access

Memory,同步动态随机存储器)也就是通常所说的内存。内存的工作原理、控制时序、及相关控制器的配置方法一直是嵌入式系统学习、开发过程中的一个难

点。我们从其硬件的角度来分析其原理,然后再引出SDRAM的驱动编写过程。

内存是代码的执行空间,以PC机为例,程序是以文件的形式保存在硬盘里面的,程序

在运行之前先由操作系统装载入内存中,由于内存是RAM(随机访问存储器),可以通过地址去定位一个字节的数据,CPU在执行程序时将PC的值设置为程序

在内存中的开始地址,

CPU会依次的从内存里取址,译码,执行,在内存没有被初始化之前,内存好比是未建好的房子,是不能读取和存储数据的,因此我们要想让MTOS运行在内存

里必须进行内存的初始化。

通用存储设备:

在介绍内存工作原理之前有必要了解下存储设备的存储方式:ROM,RAM

l ROM(Read-Only

Memory):只读存储器,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦储存资料就无法再将之改变或删除。通常用在不需经常变更资料的

电子或电脑系统中,资料并且不会因为电源关闭而消失。如:PC里面的BIOS。

l RAM(Random Access Memory)

:随机访问存储器,存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。可以理解为,当你给定一个随机有效的访问地

址,RAM会返回其存储内容(随机寻址),它访问速度与地址的无关。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间内随机访问使用的程序。计

算机系统里内存地址是一个四字节对齐的地址(32位机),CPU的取指,执行,存储都是通过地址进行的,因此它可以用来做内存。

RAM按照硬件设计的不同,随机存储器又分为DRAM(Dynamic RAM)动态随机存储器和SRAM(Static

RAM) 静态随机存储器。

l

DRAM

:它的基本原件是小电容,电容

可以在两个极板上短时间内保留电荷,可以通过两极之间有无电压差代表计算机里的0和1,由于电容的物理特性,要定期的为其充电,否则数据会丢失。对电容的

充电过程叫做刷新,但是制作工艺较简单,体积小,便于集成化,经常做为计算机里内存制作原件。比如:PC的内存,SDRAM, DDR,

DDR2, DDR3等,缺点:由于要定期刷新存储介质,存取速度较慢。

l SRAM:它是一种具有静止存取功能的

内存,不需要刷新电路即能保存它内部存储的数据。因此其存取速度快,但是体积较大,功耗大,成本高,常用作存储容量不高,但存取速度快的场合,比如CPU

的L1 cache,L2cache(一级,二级缓存) ,寄存器。

为了满足开发的需要MINI2440在出厂时搭载了三种存储介质:

(1)NOR FLASH(2M):ROM存储器,通常用来保存BootLoader,引导系统启动

(2)NAND

FLASH(256M,型号不一样,Nandflash大小不一样):保存操作系统映像文件和文件系统

(3)SDRAM(64M):内存,执行程序

l NORFLASH:它的特点是支持 XIP芯片内执行(eXecute

In Place),这样应用程序可以直接在Flash闪存内运行,不必再把代码读到系统RAM中,也就是说可以随机寻址。NOR

FLASH的成本较高。

l NAND

FLASH:它能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。其成本较低,不支持XIP。可做嵌入式里的数据存储介质。如:手

机存储卡,SD卡等。

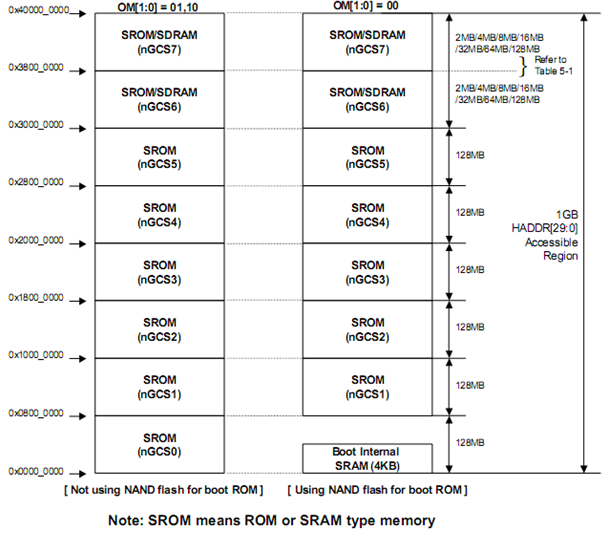

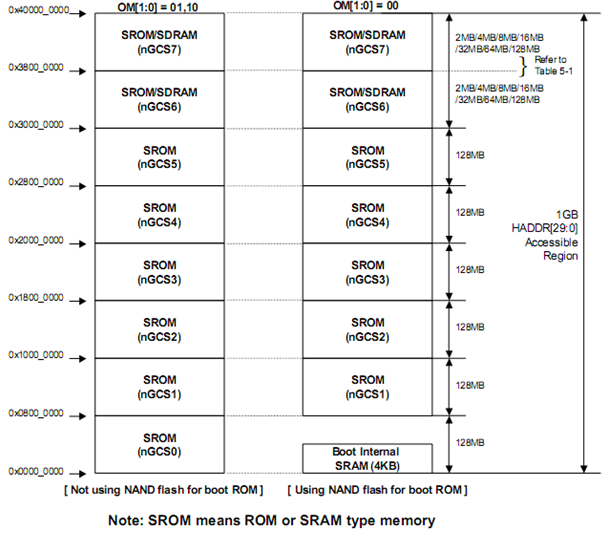

1.1.1 S3C2440存储器地址段(Bank)

S3C2440对外引出了27根地址线ADDR0~ADDR26,它最多能够寻址

128MB,而S3C2440的寻址空间可以达到1GB,这是由于S3C2440将1GB的地址空间分成了8个BANKS(Bank0~Bank7),其

中每一个BANK对应一根片选信号线nGCS0~nGCS7,当访问BANKx的时候,nGCSx管脚电平拉低,用来选中外接设备,

S3C2440通过8根选信号线和27根地址线,就可以访问1GB。如图2-48所示。

图2-48 S3C2440存储器BANK

如图所示,左侧图对应不使用Nandflash启动时(通过跳线设置),存储器

Bank分布图,通常在这种启动方式里选择Norflash启动,将Norflash焊接在Bank0,

系统上电后,CPU从Bank0的开始地址0x00000000开始取指运行。

上图右侧是选择从Nandflash引导启动(通过跳线设置),系统上电

后,CPU会自动将Nandflash里前4K的数据复制到S3C2440内部一个4K大小

SRAM类型存储器里(叫做Steppingstone),然后从Steppingstone取指启动。

其中Bank0~Bank5可以焊接ROM或SRAM类型存储

器,Bank6~Bank7可以焊接ROM,SRAM,SDRAM类型存储器,也就是说,S3C2440的SDRAM内存应该焊接在

Bank6~Bank7上,最大支持内存256M,Bank0~Bank5通常焊接一些用于引导系统启动小容量ROM,具体焊接什么样存储器,多大容量,

根据每个开发板生产商不同而不同,比如MINI2440开发板将2M的Norflash焊接在了Bank0上,用于存放系统引导程序

Bootloader,将两片32M,16Bit位宽SDRAM内存焊接在Bank6和Bank7上,并联形成64M,32位内存。

由于S3C2440是32位芯片,理论上讲可以达到4GB的寻址范围,除去上述8

个BANK用于连接外部设备,还有一部分的地址空间是用于设备特殊功能寄存器,其余地址没有被使用。

表2-14 S3C2440设备寄存器地址空间

外接设备

|

起始地址

|

结束地址

|

存储控制器

|

0x48000000

|

0x48000030

|

USB Host控制器

|

0x49000000

|

0x49000058

|

中断控制器

|

0x4A000000

|

0x4A00001C

|

DMA

|

0x4B000000

|

0x4B0000E0

|

时钟和电源管理

|

0x4C000000

|

0x4C000014

|

LCD控制器

|

0x4D000000

|

0x4D000060

|

NAND FLASH控制器

|

0x4E000000

|

0x4E000014

|

摄像头接口

|

0x4F000000

|

0x4F0000A0

|

UART

|

0x50000000

|

0x50008028

|

脉宽调制计时器

|

0x51000000

|

0x51000040

|

USB设备

|

0x52000140

|

0x5200026F

|

WATCHDOG计时器

|

0x53000000

|

0x53000008

|

IIC控制器

|

0x54000000

|

0x5400000C

|

IIS控制器

|

0x55000000

|

0x55000012

|

I/O端口

|

0x56000000

|

0x560000B0

|

实时时钟RTC

|

0x57000040

|

0x5700008B

|

A/D转换器

|

0x58000000

|

0x58000010

|

SPI

|

0x59000000

|

0x59000034

|

SD接口

|

0x5A000000

|

0x5A000040

|

AC97音频编码接口

|

0x5B000000

|

0x5B00001C

|

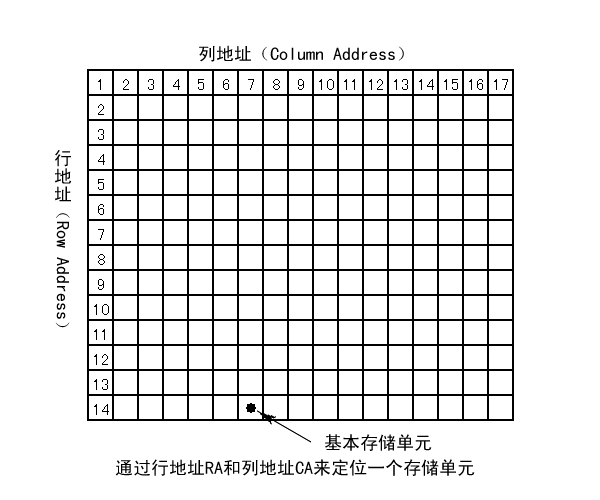

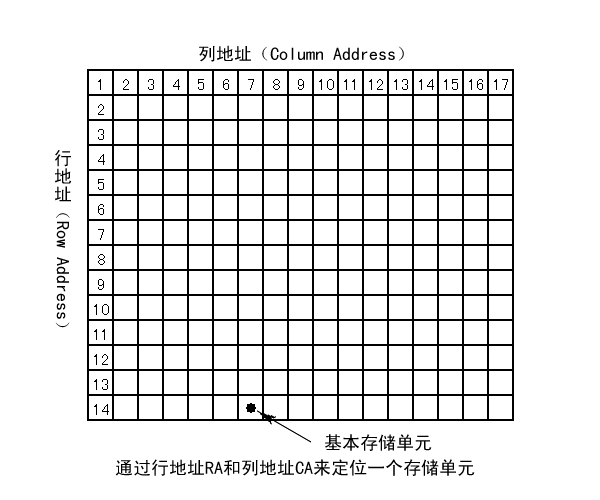

1.1.2 SDRAM内存工作原理

SDRAM的内部是一个存储阵列。阵列就如同表格一样,将数据“填”进去。在数据

读写时和表格的检索原理一样,先指定一个行(Row),再指定一个列

(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理,如图2-49所示。

图2-49内存行,列地址寻址示意图

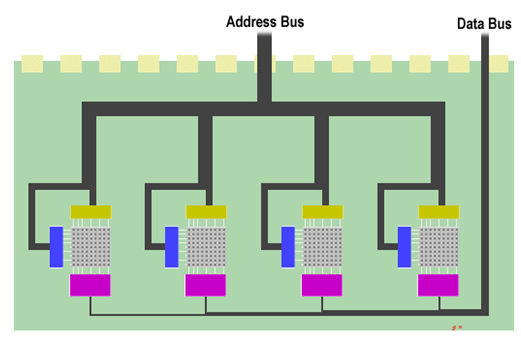

这个单元格(存储阵列)就叫逻辑 Bank(Logical Bank,下文简称 L-Bank)。

由于技术、成本等原因,不可能只做一个全容量的 L-Bank,而且最重要的是,由于 SDRAM的工作原理限制,单一的 L-Ban

k将会造成非常严重的寻址冲突,大幅降低内存效率。所以人们在 SDRAM内部分割成多个 L-Bank,目前基本都是

4个(这也是SDRAM规范中的最高L-Bank数量),由此可见,在进行寻址时就要先确定是哪个 L-Bank,然后在这个选定的

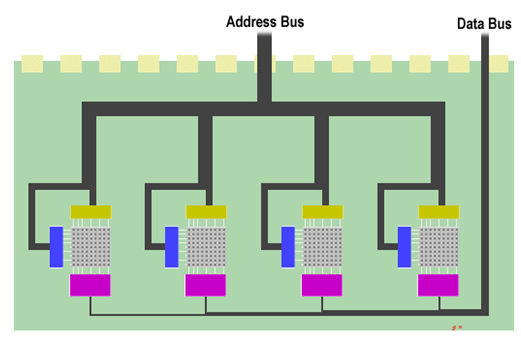

L-Bank中选择相应的行与列进行寻址。因此对内存的访问,一次只能是一个 L-Bank工作。如图2-50:

图2-50内存存储单元

当对内存进行操作时(见下图),先要确定操作L-Bank,因此要对L-Bank

进行选择。在内存芯片的外部管脚上多出了两个管脚BA0, BA1,用来片选4个L-Bank。如前所述,

32位的地址长度由于其存储结构特点,分成了行地址和列地址。通过下面的内存结构图可知,内存外接管脚地址线只有13根地址线A0~A12,它最多只能寻

址8M内存空间,到底使用什么机制来实现对64M内存空间进行寻址的呢?SDRAM的行地址线和列地址线是分时复用的,即地址要分两次送出,先送出行地址

(nSRAS行有效操作),再送出列地址(nSCAS列有效操作)。这样,可以大幅度减少地址线的数目,提高器件的性能和制作工艺复杂度。但寻址过程也会

因此而变得复杂。实际上,现在的SDRAM一般都以L-Bank为基本寻址对象的。由L-Bank地址线BAn控制L-Bank间的选择,行地址线和列地

址线贯穿连接所有的L-Bank,每个L-Bank的数据的宽度和整个存储器的宽度相同,这样,可以加快数据的存储速度。同时,BAn还可以使未被选中的

L-Bank工作于低功耗的模式下,从而降低器件的功耗。

图2-51 HY57561620内部结构图

开发板内存控制器管脚接线(以MINI2440开发板为例):

(1)确定BA0、BA1的接线

表2-15 BA0、BA1接线

图2-51 HY57561620内部结构图

开发板内存控制器管脚接线(以MINI2440开发板为例):

(1)确定BA0、BA1的接线

表2-15 BA0、BA1接线

Bank Size:

外接内存容量大小(HY57561620是4Mbit*16bit*4Bank*2Chips/8=64MB)

Bus Width: 总线宽度 (两片16位HY57561620,并联成32位)

Bank Size:

外接内存容量大小(HY57561620是4Mbit*16bit*4Bank*2Chips/8=64MB)

Bus Width: 总线宽度 (两片16位HY57561620,并联成32位)

Base Component:单个芯片容量(bit)(256Mb)

Memory Configration:内存配置 ((4M*16*4banks)*2Chips )

由硬件手册Bank

Address管脚连接配置表可知,使用A[25:24]两根地址线作为Bank片选信号,正好两根接线可以片选每个存储单元的4个BANKS。

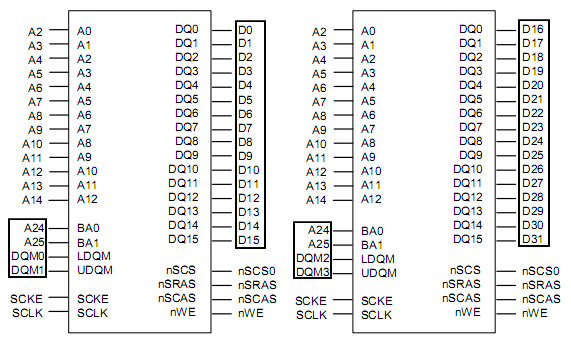

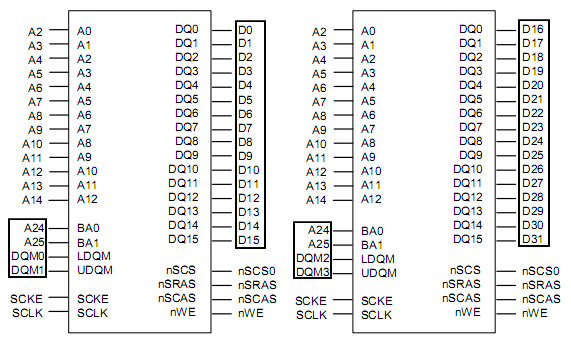

(2)确定其它接线

SDRAM内存是焊接在BANK6~BANK7上的,其焊接管脚,如图2-52:

图2-52 S3C2440 16位宽内存芯片

上图是S3C2440提供的两片16位芯片并联连接示意图,An是CPU地址总

线,其中A2~A14为内存芯片寻址总线,之所以地址寻址总线从A2开始是因为内存地址都是按字节对齐的,,A24,A25为L-Bank片选信号,Dn

为CPU数据总线,其它为对应控制信号线。

表2-16 内存芯片各管脚说明

图2-52 S3C2440 16位宽内存芯片

上图是S3C2440提供的两片16位芯片并联连接示意图,An是CPU地址总

线,其中A2~A14为内存芯片寻址总线,之所以地址寻址总线从A2开始是因为内存地址都是按字节对齐的,,A24,A25为L-Bank片选信号,Dn

为CPU数据总线,其它为对应控制信号线。

表2-16 内存芯片各管脚说明

外接管脚名

|

内接管脚名

|

全称

|

描述

|

A2~A14

|

A0~A12

|

Address

|

地址线

|

D0 ~D31

|

DQ0~DQ31

|

Data Input/Output

|

数据线

|

A24,A25

|

BA0,BA1

|

Bank Address

|

L-BANK片选信号

|

DQM0~DQM3

|

LDQM, UDQM

|

Data Input/Output Mask

|

高,低字节数据掩码信号

|

SCKE

|

SCKE

|

Clock Enable

|

输入时钟有效信号

|

SCLK

|

SCLK

|

Clock

|

输入时钟

|

nSCS0

|

nSCS

|

General Chip Select

|

片选信号(它与nGCS6是同一管脚的两个功能)

|

nSRAS

|

nSRAS

|

Row Address Strobe

|

行地址选通信号

|

nSCAS

|

nSCAS

|

Column Address Strobe

|

列地址选通信号

|

nWE

|

newnWE

|

Write Enable

|

写入有效信号

|

我们通过S3C2440 16位宽内存芯片接线图可以看出,两片内存芯片只有两个地方不一样,LDQM,

UDQM和数据总线DQn接线方式不一样。

由于存储芯片位宽为16位,一次可以进行两个字节的读取。但是,通常操作系统里最

小寻址单位是1字节,因此内存控制器必须要保证可以访问内存里每一个字节。UDQM

,LDQM分别代表16位数据的高,低字节读取信号,当读取数据时,LDQM

/UDQM分别用来控制16位数据中高低字节能否被读取,当LDQM /UDQM为低电平时,对应的高/低字节就可以被读取,如果LDQM

/UDQM为高电平时,对应的高/低字节就不能被读取。当向内存里写入数据时,LDQM /UDQM控制数据能否被写入,当LDQM

/UDQM为低电平时,对应的高/低字节就可以被写入,如果LDQM /UDQM为高电平时,对应的高/低字节就不能被写入。通过对LDQM

/UDQM信号的控制可以控制对两个存储芯片存储数据,由于两个存储单元的地址线是通用的,他们都能接收到CPU发出的地址信号,但是,发给两个存储单元

的LDQM /UDQM信号是不同的,以此来区分一个字的高低字节。

S3C2440A为32位CPU,也就是说其数据总线和地址总线宽度都是32位

(可以理解为32根线一端连接CPU内部,另外一端连接向内存控制器),那么内存数据的输入/输出端也要保证是32位总线,MINI2440上采用两片

16位宽总线内存芯片并联构成32位总线。其中一个芯片连接到CPU数据总线的低16位,另外一个芯片连接到数据总线上的高16位,并联成32位总线,因

此两个芯片的输入/输出总线连接到CPU总线上的不同管脚上。

1.1.3